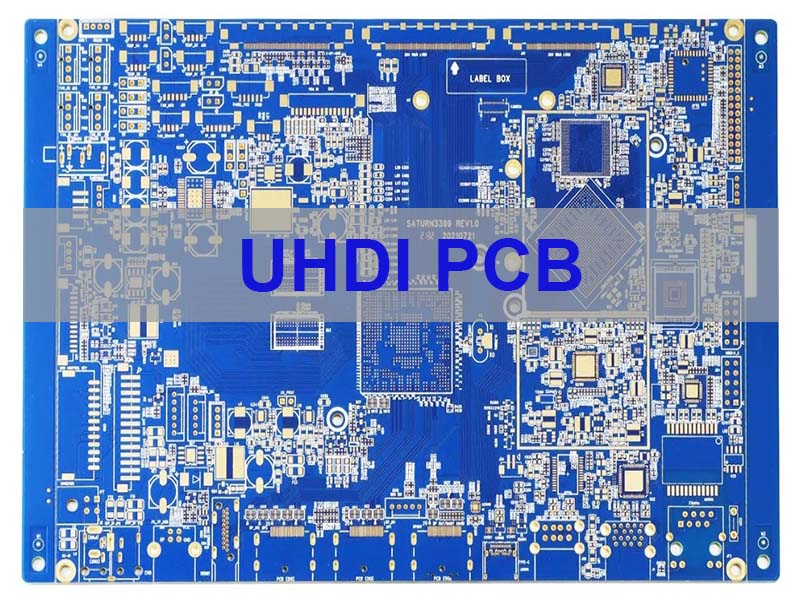

UHDI PCB represents the pinnacle of high-density interconnect technology, enabling the advanced miniaturization and superior performance required by next-generation electronics. This comprehensive guide delves into everything you need to know about UHDI PCBs, from their fundamental definition and materials to design considerations and how to select the right manufacturing partner for your prototype and production needs.

What are the core pain points when sourcing UHDI PCBs?

- Finding True Expertise: Many manufacturers claim HDI capability, but few possess the specialized equipment and process control for genuine UHDI features like 25µm line/space and microvias below 50µm.

- Prototype Delays: Critical R&D and testing phases are stalled by long lead times for complex UHDI prototypes, delaying time-to-market for cutting-edge products.

- Unpredictable Costs: Opaque pricing structures and unexpected engineering charges for impedance control and advanced materials like Megtron 6 or Rogers make budgeting difficult.

- Design for Manufacturing (DFM) Gaps: A lack of proactive engineering support leads to design revisions, respins, and failures because the board wasn’t optimized for UHDI fabrication processes.

- Fragmented Supply Chain: Managing separate vendors for design, PCB fabrication, assembly, and testing adds complexity, risk, and communication overhead.

Best Technology provides integrated solutions to these exact challenges. As a specialized UHDI PCB manufacturer, we bridge the gap between ambitious design and reliable, high-yield manufacturing.

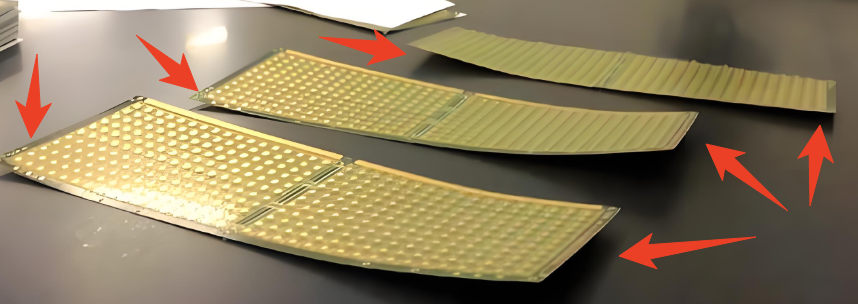

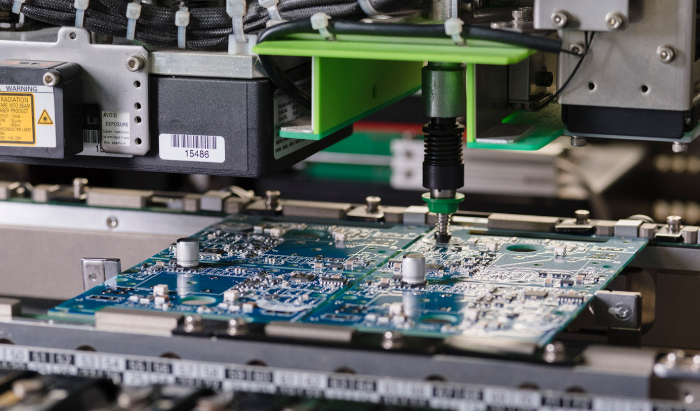

- Proven UHDI Process Mastery: Our investment in technology like laser direct imaging and advanced laser drilling allows us to reliably produce 2/2 mil lines and 0.1mm microvias, meeting the stringent demands of UHDI circuits.

- Rapid Prototype Service: We prioritize quick-turn UHDI PCB prototype fabrication, with expedited services available to get your boards in hand for testing in as little as 48-72 hours for multilayer builds, accelerating your development cycle.

- Transparent and Competitive Pricing: We offer clear, upfront quotations for prototype and volume production, with cost breakdowns for different quantities (e.g., 1 pc, 100 pcs, 1000 pcs) and materials, ensuring no surprises.

- Expert DFM and Stack-up Support: Our engineering team works with you from the start, providing preliminary stack-up structures and impedance modeling guidance (e.g., for 80 GHz applications) to ensure your design is manufacturable and performs as intended.

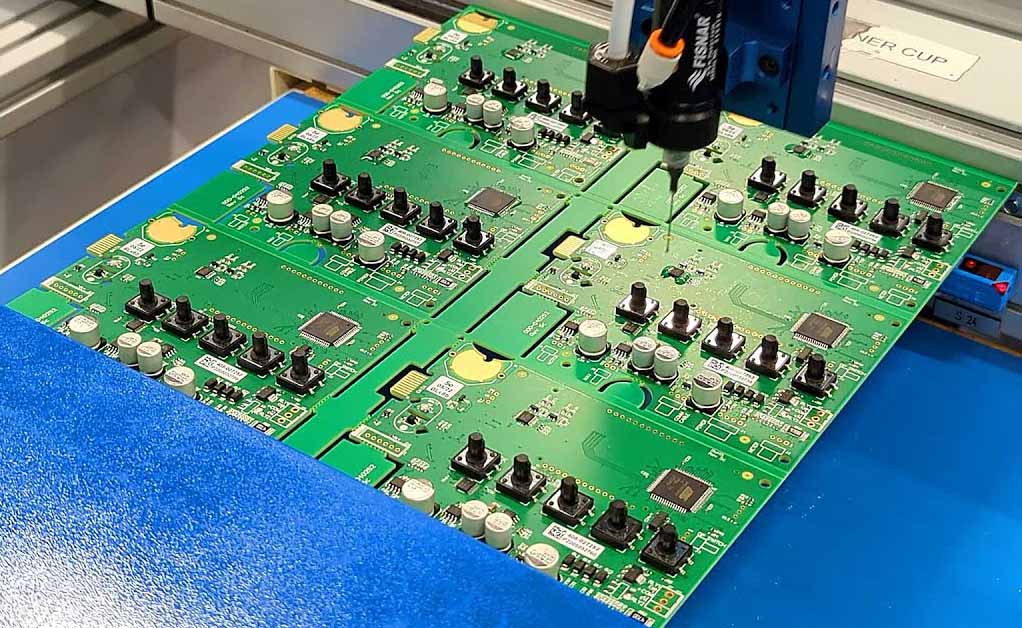

- Full Turnkey Service: From UHDI printed circuit board fabrication and component sourcing to precise assembly and rigorous testing, we offer a one-stop solution, simplifying your supply chain and ensuring accountability.

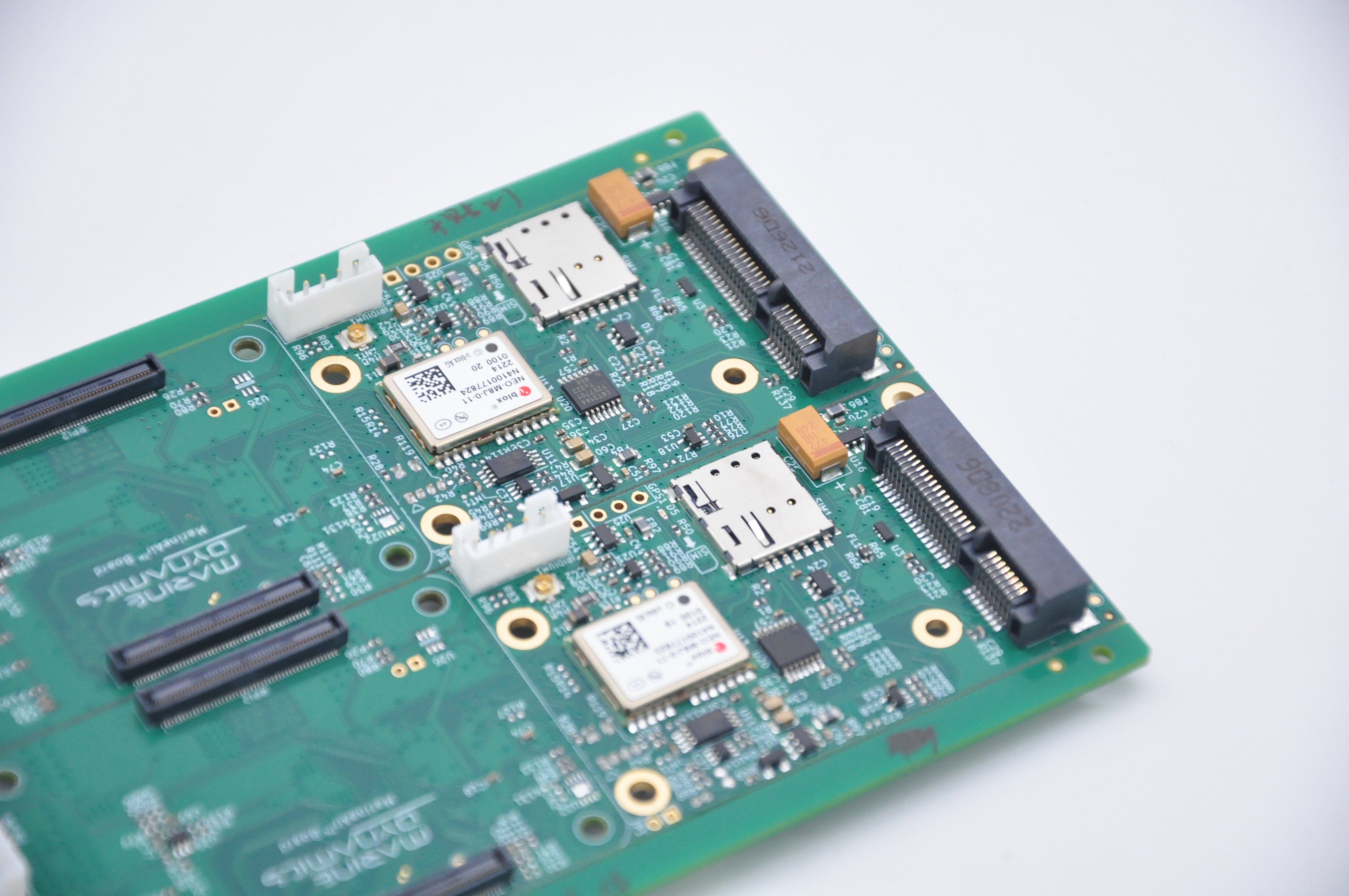

EBest Circuit (Best Technology) is a premier and experienced UHDI PCB manufacturer in China. With 20 years of dedicated PCB fabrication expertise, we have evolved into a trusted full-turnkey solution provider. We specialize in advanced technologies including UHDI, RF/microwave PCBs (using Rogers, Taconic, Megtron materials), heavy copper, and rigid-flex boards. Our commitment is underscored by ISO9001, IATF16949, and ISO13485 certifications, and a 97% on-time delivery rate. We combine state-of-the-art equipment with deep engineering knowledge to deliver high-quality, high-precision PCBs for the most demanding applications. For your UHDI project, pls feel free to contact our experts at sales@bestpcbs.com.

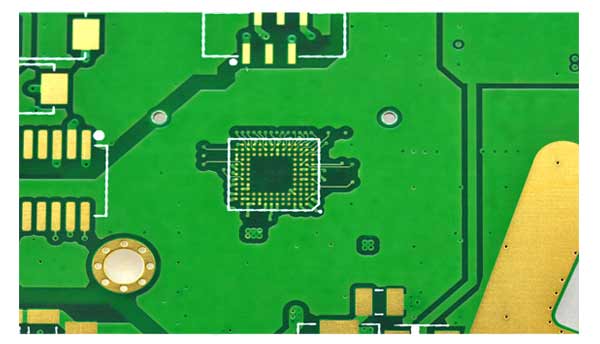

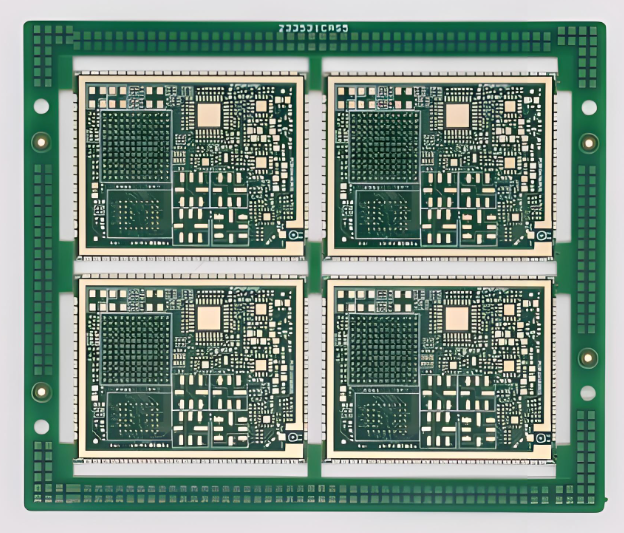

What Is a UHDI PCB?

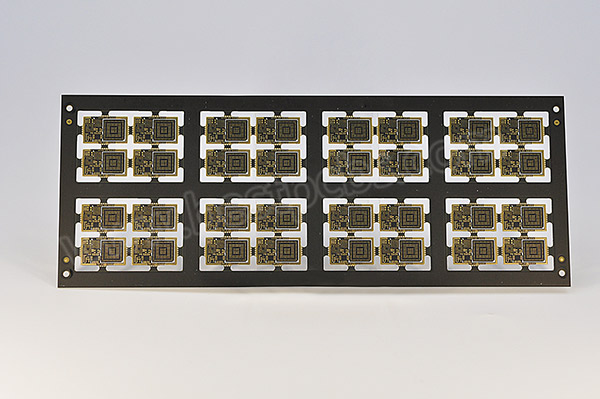

A UHDI (Ultra High-Density Interconnect) PCB is an advanced type of printed circuit board characterized by exceptionally fine features, which enable a dramatically higher wiring density within a given area compared to standard HDI or traditional PCBs. This is achieved through extremely narrow trace widths/spacing, smaller microvias, and higher interconnect pad density.

Key characteristics defining a UHDI circuit board include:

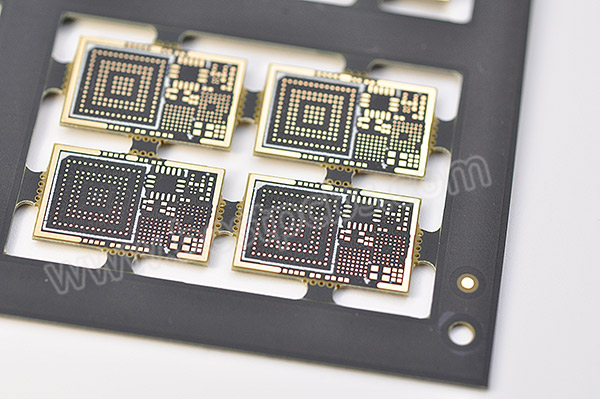

- Extremely Fine Lines/Spaces: Feature sizes of 30µm (1.2 mil) and below, pushing towards 25µm (1 mil) or less. Our capabilities support advanced HDI features down to 2/2 mil.

- Microvias: Extensive use of laser-drilled microvias with diameters below 75µm (3 mil), often in stacked or staggered configurations. Our equipment allows for minimum laser-drilled via diameters of 4 mil (0.1mm).

- High Layer Count: Often involves 10+ layers to accommodate complex routing in compact spaces. We can manufacture up to 32-layer multilayer boards.

- Advanced Materials: Frequent use of high-performance, low-loss laminate materials to ensure signal integrity at high speeds.

- Any-Layer Interconnection: The most advanced form where microvias can connect any two layers in the stack-up, maximizing routing freedom.

In essence, a UHDI printed circuit board (PCB) is the enabling hardware for today’s most compact and high-performance electronic devices, such as advanced smartphones, wearable technology, and high-speed computing modules, where real estate is at a premium and signal speeds are critical.

What Is the Difference Between a UHDI PCB and an HDI PCB?

While both HDI (High-Density Interconnect) and UHDI PCBs aim to increase wiring density, UHDI represents a significant evolution and a higher tier of capability. Think of HDI as the foundation and UHDI as the specialized, cutting-edge extension of that technology.

The primary differences are quantitative and qualitative advances in manufacturing tolerances and design rules:

| Feature | HDI PCB | UHDI PCB |

|---|---|---|

| Line/Space (Typical) | 3/3 mil (75/75 µm) and above | 2/2 mil (50/50 µm) and below, targeting ≤1/1 mil |

| Microvia Diameter | ≥4 mil (100 µm) | ≤3 mil (75 µm), targeting 1-2 mil |

| Pad Size | Relatively larger | Extremely small, often at the limit of registration accuracy |

| Interconnect Density | High | Ultra-High |

| Primary Driver | Space saving, moderate performance | Maximum miniaturization, highest signal integrity for high-speed/frequency |

| Manufacturing Process | Advanced laser drilling, sequential lamination | Same as HDI, but with tighter process control, more advanced imaging (e.g., LDI), and often more lamination cycles. |

In summary, all UHDI PCBs are HDI, but not all HDI PCBs qualify as UHDI. UHDI pushes the boundaries of HDI technology to its extremes, requiring more precise and controlled manufacturing processes. For instance, our standard HDI capability offers 3/3 mil lines, while our advanced processes support the 2/2 mil features that edge into UHDI territory, demonstrating the technical progression.

What Is the Difference Between a UHDI PCB and an RF PCB?

This is a crucial distinction: UHDI and RF PCB are classifications based on different primary objectives. One focuses on density, the other on signal performance at high frequencies. They are not mutually exclusive and often converge in advanced applications.

| Aspect | UHDI PCB | RF PCB |

|---|---|---|

| Primary Goal | Maximize density & miniaturization. | Signal integrity at high frequency. |

| Key Metric | Fine features (line/space, via density). | Material properties (Dk/Df). |

| Critical Materials | Advanced FR4, thin cores. | Specialized low-loss laminates (e.g., Rogers, Megtron). |

| Design Focus | Routing complexity & microvias. | Transmission line geometry & grounding. |

| Typical Applications | Mobile, wearable, compact devices. | 5G/6G, radar, satellite comms. |

The convergence of these two technologies results in what is known as an RF UHDI PCB. The most advanced boards, like the one mentioned in the customer inquiry for 80 GHz operation, must be both. They require the ultra-fine features of UHDI to route high-density, high-pin-count RF components and the specialized materials (like Megtron 6 or Rogers) of an RF PCB to maintain signal integrity at such extreme frequencies. Manufacturing such a board requires a vendor proficient in both domains—handling advanced materials with precise impedance control while executing UHDI-level fine features and microvia structures.

What Material Is a UHDI PCB Made Of?

The materials for a UHDI PCB are selected to support both the fine-feature fabrication processes and the intended electrical performance, often high-speed or high-frequency.

Core Material Systems:

- Standard & High-Performance FR4: For UHDI applications not at the extreme high-frequency edge, high-Tg FR4 (Tg ≥ 170°C) like KB6167 or IT180 is common. It offers good stability for sequential lamination cycles. Our material inventory includes high-Tg, no-halogen FR4 options suitable for complex multilayers.

- Low-Loss / High-Speed Laminates: For UHDI boards where signal integrity is paramount, materials with a lower dissipation factor (Df) are mandatory. This includes:

- Megtron 6/7/8 (Panasonic): A popular choice for high-speed digital and RF applications, offering excellent electrical properties.

- Rogers RO4000® Series: Ceramic-filled hydrocarbon laminates ideal for RF and microwave designs.

- Isola FR408HR, Nelco N4000-13: Other high-performance options for demanding electrical environments.

- Thin Dielectric Laminates and Prepregs: UHDI relies on very thin core and prepreg layers (e.g., 1080, 106, 1035 styles) to achieve the close layer spacing needed for microvias and controlled impedance in dense layouts. We utilize a wide range of PP types, including 1080 (0.07mm), 2116 (0.11mm), and 7628 (0.175mm).

- Advanced Copper Foils: Treated or very low-profile copper foils are used to improve adhesion and etching yields for extremely fine traces.

The choice of material is dictated by the application’s frequency, data rate, thermal, and reliability requirements. For the 80 GHz application specified in the inquiry, Megtron 6 or Rogers would be the recommended substrate materials to meet the low-loss demands at that frequency, fabricated using UHDI processes.

How to Design the Preliminary Stack-Up Structure of a UHDI Printed Circuit Board?

Designing the stack-up is a foundational step in UHDI PCB development, critical for impedance control, signal integrity, power integrity, and manufacturability. A well-planned stack-up saves multiple prototyping cycles.

A step-by-step approach for a preliminary UHDI PCB stack-up design:

- Define Requirements: Start with the board’s functional needs: number of signal layers, power/ground planes, target impedance (e.g., 50Ω single-ended, 100Ω differential), operating frequency (e.g., 80 GHz), and board thickness constraints.

- Select Core Material: Based on frequency/speed, choose the dielectric material (e.g., Megtron 6 for RF, High-Tg FR4 for high-density digital). Obtain its certified Dk and Df values at your target frequency from the manufacturer’s datasheet.

- Determine Dielectric Thickness: This is the distance between adjacent copper layers. For UHDI, these are often very thin (e.g., 2-4 mils) to enable microvias and tight coupling. Use an impedance calculator (like Polar Si9000) with the material Dk, target impedance, and desired trace width to solve for the required dielectric thickness.

- Choose Copper Weight: Thinner copper (e.g., ½ oz or 1/3 oz) is preferred for etching fine traces. Standard UHDI designs often use ½ oz (17.5 µm) finished copper for signal layers. Heavier copper (1 oz+) may be used for power planes.

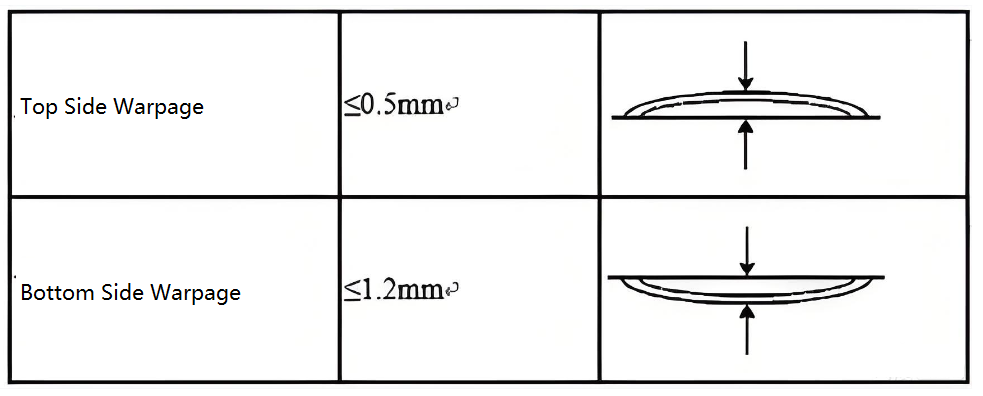

- Arrange Layer Sequence: Follow a symmetrical stack-up to prevent warpage. Use a signal-ground-signal (S-G-S) sandwich for critical high-speed lines to provide a clear return path. Place power and ground planes adjacent to each other to form a decoupling capacitor.

- Plan the Via Strategy: Decide on via types: through-hole vias, blind vias (from surface to inner layer), buried vias (between inner layers), and microvias (typically <6 mil diameter). In UHDI, microvias are key. Plan their depth (1-n layers) and whether they will be stacked or staggered.

- Consult Your Manufacturer Early: Engage with your UHDI PCB manufacturer (like Best Technology) during this phase. Share your target stack-up for a DFM review. We can provide feedback on material availability, feasible dielectric thicknesses, and recommend adjustments for optimal yield and performance.

Example Preliminary Stack-Up for a 12-Layer UHDI/RF Board:

| Layer | Type | Material/Thickness | Description |

|---|---|---|---|

| L1 | Signal | ½ oz Cu | Top Layer, RF Components |

| Dielectric | 3.5 mil Megtron 6 | ||

| L2 | Ground | 1 oz Cu | Solid Ground Plane |

| Dielectric | 4 mil Prepreg | ||

| L3 | Signal | ½ oz Cu | High-Speed Signals |

| Core | 4 mil Megt6 Core | ||

| L4 | Power | 1 oz Cu | Power Plane 1 |

| … | … | … | … |

| L12 | Signal | ½ oz Cu | Bottom Layer |

This is a simplified example. The actual design would be built in collaboration with our engineers.

Where Is a UHDI PCB Used?

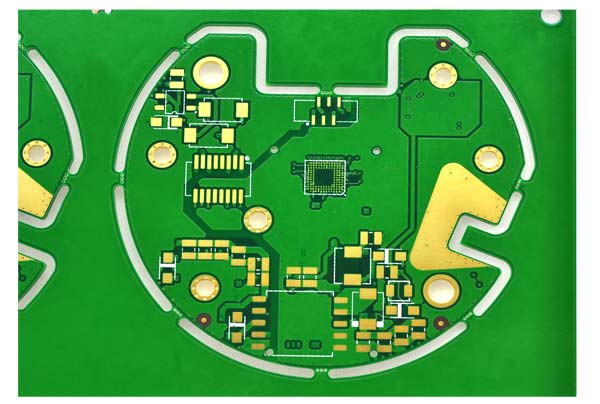

UHDI PCBs are indispensable in industries where miniaturization, high performance, and reliability are non-negotiable. Their ability to pack immense functionality into a tiny footprint makes them the backbone of modern advanced electronics.

Primary application areas for UHDI printed circuit boards include:

- Consumer Electronics: Smartphones, tablets, laptops, and wearables (smartwatches, AR/VR headsets) constantly push for smaller, lighter, and more powerful devices.

- Medical Electronics: Implantable devices (pacemakers, neurostimulators), advanced diagnostic imaging equipment, and miniature surgical tools.

- Telecommunications & 5G/6G Infrastructure: RF front-end modules, millimeter-wave antennas, base station processing units, and network switches operating at extremely high frequencies.

- Automotive Electronics: Advanced Driver-Assistance Systems (ADAS), LiDAR sensors, infotainment systems, and vehicle control units in electric and autonomous vehicles.

- Aerospace and Defense: Avionics, satellite communication systems, radar, and guidance systems where reliability and performance in harsh environments are critical.

- High-Performance Computing (HPC): Servers, data centers, and AI accelerator modules that require high-speed data transfer between densely packed components.

In each case, the UHDI circuit board enables a critical size reduction or performance enhancement that would be impossible with conventional PCB technology.

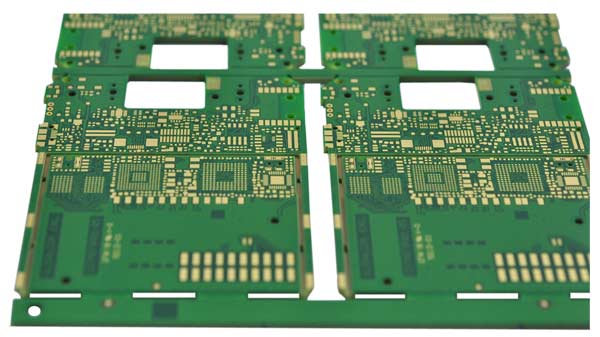

Top 10 UHDI Circuit Board Manufacturers in China

Identifying the “top” manufacturers depends heavily on specific project needs—prototype vs. volume, technology focus (e.g., RF UHDI), and industry vertical. Rather than a simple list, here are key criteria for evaluation and how Best Technology positions itself:

Key Evaluation Criteria for a UHDI PCB Manufacturer:

- Technology Certification: Demonstrated capability in ≤ 3/3 mil line/space, microvia drilling ≤ 4 mil, and any-layer HDI processes. We support 2/2 mil lines and 4 mil (0.1mm) laser-drilled microvias.

- Material Expertise: Proven experience with high-frequency laminates (Rogers, Taconic, Megtron) and high-Tg materials. Our material portfolio includes these advanced substrates.

- Advanced Equipment: Investment in LDI (Laser Direct Imaging) for fine-line patterning, high-precision laser drills, and AOI (Automatic Optical Inspection). We utilize equipment from global leaders like Hitachi (drilling) and Israeli AOI systems.

- Engineering Support: Strong DFM and stack-up design support team. Our engineers provide preliminary stack-up structures for impedance matching.

- Quality Systems: Certifications like IATF 16949 (automotive) and ISO 13485 (medical) indicate process rigor. We hold these certifications, among others.

- Prototype Speed: Willingness and ability to offer quick-turn prototype services. We provide expedited 24-72 hour turns for multilayer prototypes.

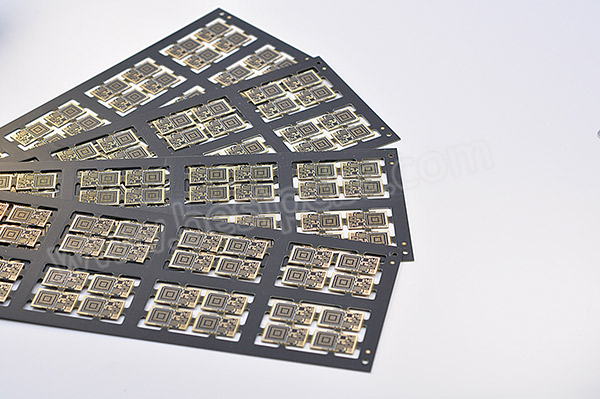

- Volume Scalability: Capacity to scale from prototype to medium/high-volume production seamlessly. Our monthly capacity is over 28,900 square meters.

- Testing Capability: In-house electrical testing, impedance testing, and reliability testing. We employ flying probe testers, universal E-testers, and micro-section analysis.

- Vertical Integration: Offering turnkey services (PCB + Assembly) reduces supply chain risk. We are a full turnkey provider.

- Customer Service & Communication: Responsive, technical sales and project management. We pride ourselves on one-on-one engineering support and fast response times.

Top 10 UHDI Circuit Board Manufacturers in China (Reference Table)

| Company | Process Capability | Prototype Lead Time |

|---|---|---|

| EBest Circuit (Best Technology) | 1+N+1 to 3+N+3; PTH ≤0.1mm | 24 hours |

| PCBWay | Microvias; 0.10mm laser hole; 55/55μm L/S | 24 hours |

| PCBCart | HDI; 2.5 mil trace/space | 2 days to 5 weeks |

| JLCPCB | Blind/buried vias; 0.15mm via hole | 24–72 hours |

| OurPCB | 2.5 mil trace/space; 0.1mm microvia | 24 hours to 7 days |

| RayPCB | 3 mil trace/space; ~150μm via | 1–5 days |

| KKPCB | 2/2 mil L/S; 0.075–0.15mm laser drill | To be confirmed |

| WellPCB | 1.8 mil spacing; microvia support | About 2 weeks |

| Weller PCB | 2/2 mil HDI; microvias <150μm | 1–2 days |

| PCBBUY | 2/2 mil HDI; ≥0.075mm blind via | 24 hours to 7 days |

Note: The ranking above is for reference only. The right UHDI PCB manufacturer should be selected based on your required line/space, microvia structure, material system, stack-up complexity, prototype speed, and volume production needs.

Why Choose EBest Circuit (Best Technology) for UHDI PCB Prototype Fabrication?

Selecting the right partner for your UHDI prototype is critical to project success. Best Technology is engineered to be that partner, offering a unique blend of advanced capability and responsive service.

- Proven Advanced Technology Foundation: Our core manufacturing capabilities are tailored for complexity. We routinely handle ultra-fine features (3/3 mil standard, 2/2 mil advanced HDI), high layer counts (up to 32 layers), and controlled impedance (tolerance ±10% for >50Ω, ±5Ω for ≤50Ω). Our expertise in heavy copper (up to 20 oz) and various substrates (FR4, MCPCB, Ceramic) translates to robust process control for delicate UHDI structures.

- Dedicated Quick-Turn Prototype Service: We understand the urgency of innovation. For standard-specification FR4 prototypes under 1 sq meter, we offer rapid turnaround (e.g., 10 days for 6-layer, 72 hours for expedited service). This service extends to complex builds, allowing you to iterate and validate designs quickly, compressing your R&D timeline.

- Comprehensive Quality and Reliability Assurance: Quality is integrated into our process. We hold ISO 9001:2015, IATF 16949:2016, and ISO 13485:2016 certifications. Our inspection regime includes Automated Optical Inspection (AOI) from industry leaders, X-ray copper thickness testers, flying probe testing, and micro-section analysis to validate every microvia and trace.

- Expert Engineering Partnership: We don’t just manufacture; we collaborate. Our engineering team provides proactive DFM feedback, assists with material selection (crucial for 80 GHz RF UHDI boards), and delivers preliminary stack-up structures for your impedance modeling. We help bridge the gap between your design and a manufacturable, high-performance product.

- Full Turnkey Solution and Support: From the initial UHDI PCB prototype quote to final box build, we provide a seamless, accountable journey. Our one-stop service covers PCB fabrication, component sourcing, PCB assembly (with capabilities for 01005 components and 0.25mm BGA pitch), and testing. You get a single point of contact, simplified logistics, and faster overall project completion.

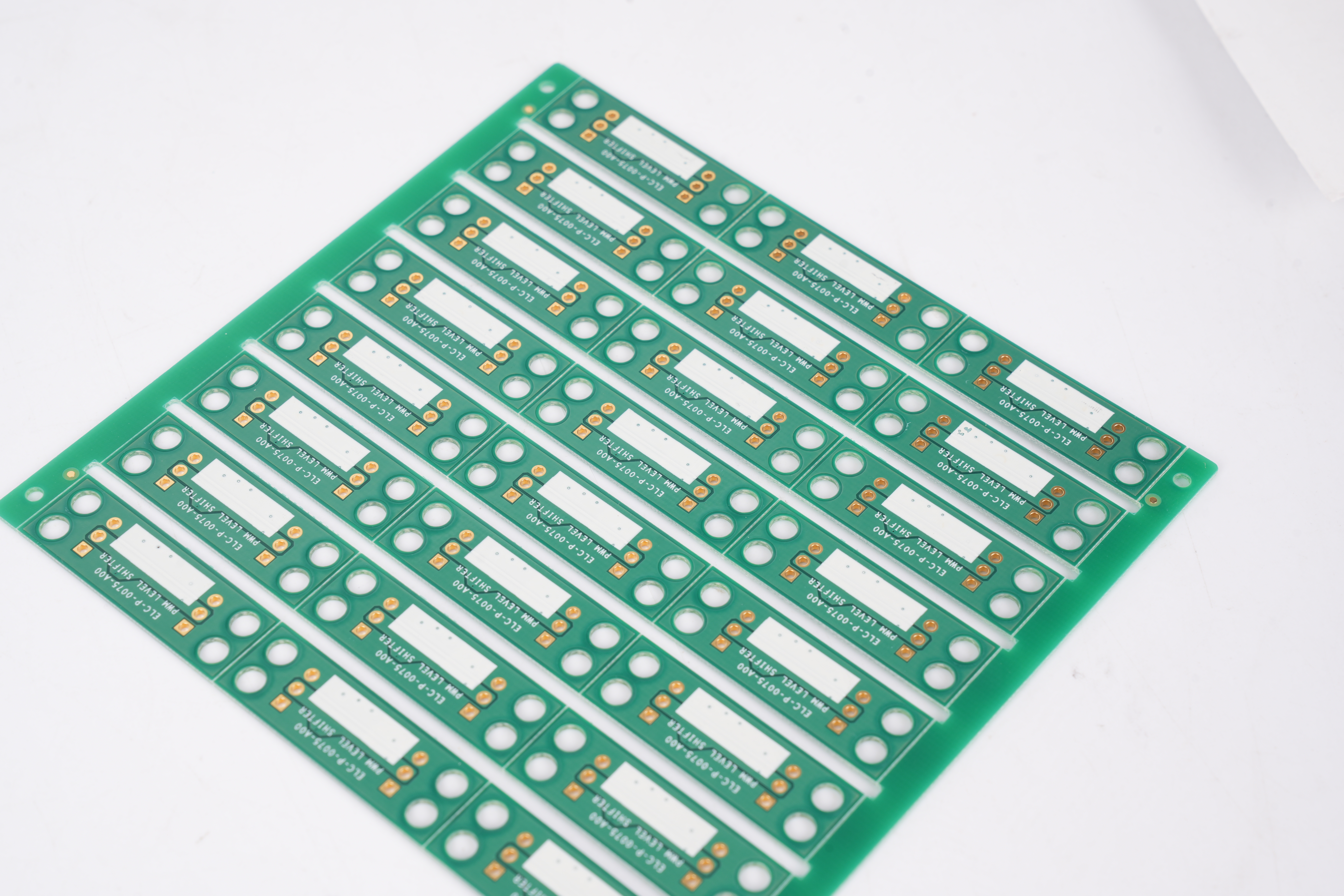

How to Request a Quote for UHDI PCB Prototype Fabrication?

Requesting a quote for a UHDI PCB is straightforward when you provide the right information. A complete and clear request ensures an accurate, fast, and competitive quotation. Here is a step-by-step guide based on common requirements, like those from the Technion inquiry:

- Prepare Your Design Files: The essential package includes your Gerber files (RS-274X format preferred), drill files, and a completed PCB fabrication drawing with all critical dimensions, tolerances, and notes.

- Specify Technical Requirements: Create a separate document detailing:

- Layer Count & Stack-up: Preferred materials (e.g., “Megtron 6 for all layers” or “Rogers 4350B for L1-L4”).

- Finished Board Thickness & Tolerance.

- Copper Weight: For inner and outer layers (e.g., ½ oz inner, 1 oz outer).

- Surface Finish: Specify one, e.g., ENIG, ENEPIG, Immersion Silver, Hard Gold (for edge connectors).

- Impedance Control: Target values, tolerance (e.g., 50Ω ±10%), and which layers/differentials are controlled.

- Special Requirements: Any specific needs like filled/via-in-pad, edge plating, or tight impedance tolerances for RF sections.

- Define Quantity and Urgency:

- Clearly state the quantities you need quotes for: Prototype quantity (e.g., 5 pcs), 100 units, and 1000 units. This allows us to show volume pricing breaks.

- Indicate your required lead time (e.g., “Standard” or “Expedited”).

- Request a Preliminary Stack-Up (if needed): If you are in the early design phase (like the 80 GHz application mentioned), you can request that we provide a preliminary stack-up structure based on your material choice and impedance targets. This allows you to perform accurate impedance modeling in your design tools.

- Submit and Engage: Send your complete package to sales@bestpcbs.com. A dedicated engineering sales person will review your files, may ask clarifying questions, and will provide a formal quotation typically within 24 hours, including unit price, volume pricing, and lead time options.

In closing, UHDI PCBs are the critical hardware foundation enabling the relentless march of electronic miniaturization and performance enhancement across industries from healthcare to telecommunications. This article has explored the what, why, and how of UHDI technology, the key differences from HDI and RF PCBs, and the practical steps involved in designing and procuring these advanced boards.

EBest Circuit (Best Technology) stands as a reliable specialist in this field. With two decades of experience, certified quality systems, advanced manufacturing capabilities supporting fine features and advanced materials, and a commitment to fast-turn prototypes and full turnkey solutions, we are equipped to bring your most challenging UHDI circuit board designs to life. Pls feel free to contact our technical sales team anytime at sales@bestpcbs.com for a comprehensive consultation and quotation.

FAQs About UHDI PCBs

1. What is the minimum line/space Best Technology can achieve for UHDI prototypes?

We regularly manufacture advanced HDI boards with 3/3 mil (75/75 µm) line/space. For designs pushing into UHDI territory, we have the capability to support 2/2 mil (50/50 µm) features, subject to a full DFM review of your specific design.

2. Can you handle the RF materials like Rogers or Megtron 6 required for high-frequency UHDI boards?

Yes, absolutely. We have extensive experience processing high-frequency, low-loss laminates including the Rogers series (e.g., RO4003C, RO4350B), Taconic, and Panasonic’s Megtron 6/7. We can guide you on material selection for applications like 80 GHz and ensure proper lamination and impedance control.

3. What is the typical lead time for a 10-layer UHDI PCB prototype?

For a standard 10-layer FR4 prototype (<1 sq. meter), our typical lead time is 12 business days. We offer expedited services that can significantly reduce this time. The lead time for a UHDI board with advanced materials (like Megtron 6) and features will be confirmed upon review of your specific technical files.

4. Do you provide impedance control and testing reports?

Yes. We have in-house impedance modeling expertise and can control impedance to tight tolerances (e.g., ±10% for values >50Ω, ±5Ω for ≤50Ω). We can provide impedance test coupons on the panel and, upon request, supply test reports to verify performance.

5. Do you offer turnkey services including component sourcing and assembly for UHDI PCBA?

Yes, we are a full turnkey provider. We can manage the entire process: manufacturing the UHDI printed circuit board, sourcing all components from authorized distributors, performing precise SMT assembly (handling 01005 components and 0.25mm BGA pitch), and conducting full functional testing. This simplifies your supply chain and ensures accountability.