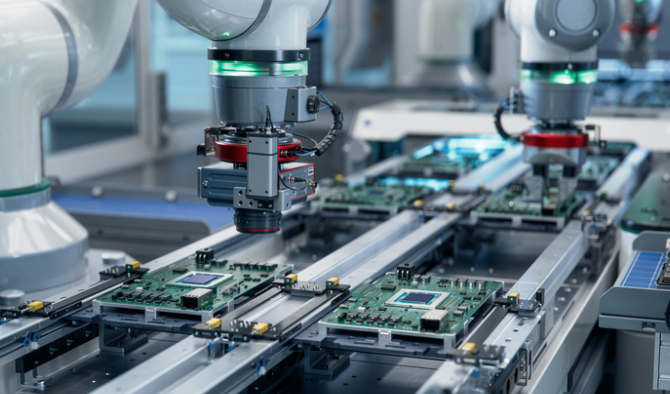

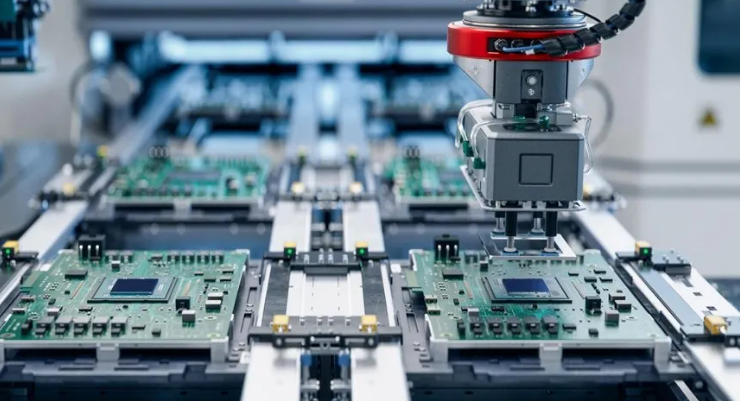

PCB assembly services Switzerland specialize in high-precision, compliant production for medical, aerospace, and industrial sectors, using advanced SMT and THT equipment paired with rigorous quality checks. These PCB assembly services Switzerland consistently meet global industry standards, addressing the specific needs of businesses requiring durable, high-performance electronic components.

Why Choose PCB Assembly Services Switzerland?

Advantages of PCB Assembly Services Switzerland:

- Stringent quality compliance: Adheres to ISO 9001:2015, ISO 13485:2016, and IPC-A-610 Class 3 standards, critical for high-reliability applications.

- Precision manufacturing capabilities: Master advanced processes like MSAP, supporting ultra-fine line/space down to 10μm and HDI boards with 30μm line widths.

- Localized supply chain efficiency: Proximity to European component suppliers reduces lead times and minimizes logistics disruptions.

- Zero-defect delivery record: Consistent compliance with EEMUA quality standards, ensuring minimal rework and project delays.

- Flexibility for small to large batches: Adapts to low-volume prototypes and high-volume production without compromising cost or speed.

- Specialization in medical and industrial sectors: Deep expertise in assembling PCBA for devices requiring extreme temperature resistance (-55°C to 125°C) and biocompatibility.

- End-to-end traceability: Full material and process tracking via MES systems, ensuring accountability and easy compliance audits.

Pain Points of PCB Assembly Services Switzerland

- Component shortage and unstable lead times: Global chip shortages and international logistics delays often disrupt material sourcing for time-sensitive projects.

- Counterfeit or refurbished component risks: Unverified suppliers may provide substandard parts, leading to batch failures and compliance violations.

- High cost for small-batch production: Tooling, setup, and testing costs are disproportionately high for low-volume orders, increasing per-unit expenses.

- Strict compliance and certification barriers: Meeting ISO 13485, RoHS, and IPC standards requires significant investment in processes and training.

- Complex process control for high-density boards: HDI and BGA assemblies demand precise equipment calibration, leading to higher defect rates without proper expertise.

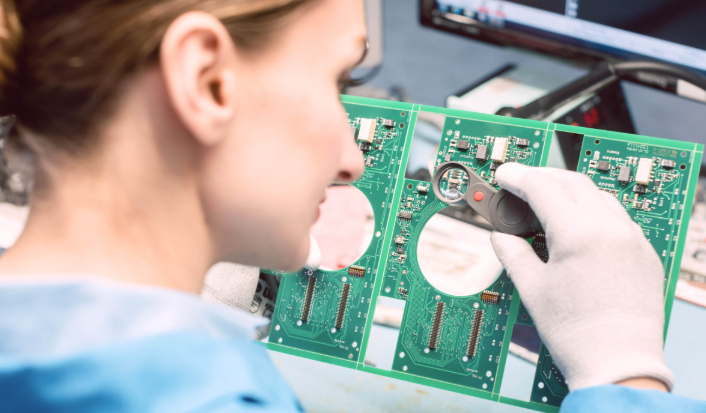

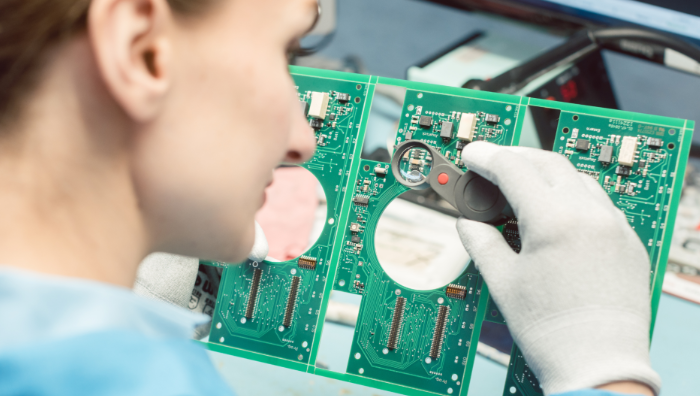

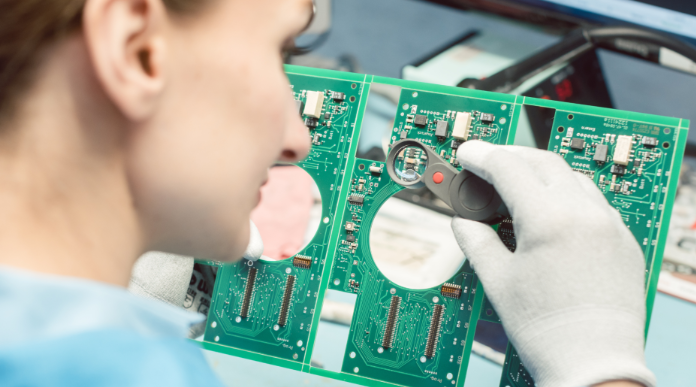

- Inadequate testing coverage: Certain board areas (e.g., component bottoms) are hard to inspect via AOI, leading to missed defects.

- Delayed delivery due to design mismatches: Lack of DFM reviews leads to design changes mid-production, extending lead times and increasing costs.

One Stop Switzerland PCBA Service: Solving Supply Chain Delays Problems

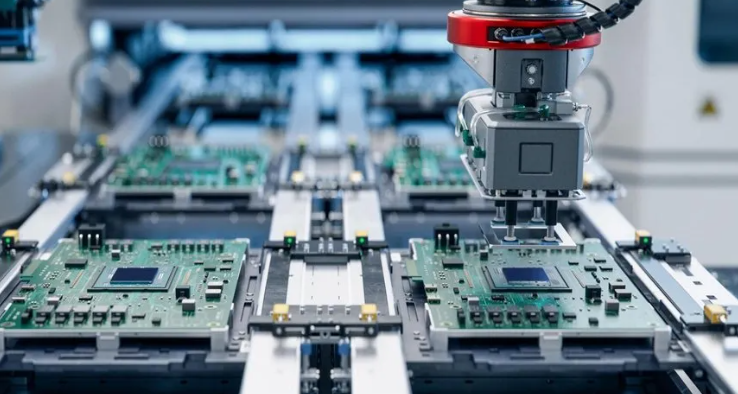

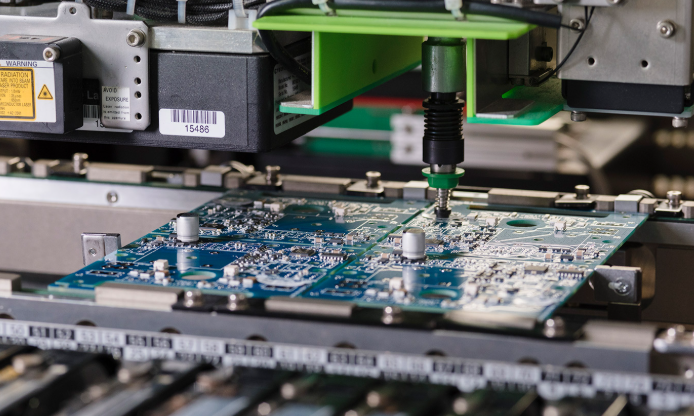

Our one-stop Switzerland PCBA service eliminates supply chain delays primarily through integrated resource synergy and streamlined supply chain management, a core strength distinguishing our services. We have established a stable cooperative network with 15+ globally verified component suppliers and built a professional intelligent component warehousing center, stocking core electronic components commonly used in medical and industrial fields. This integrated resource layout avoids risks of component shortages and long international logistics cycles, shortening component sourcing lead time from 4-6 weeks to 3-5 days and fundamentally solving delays caused by material acquisition difficulties.

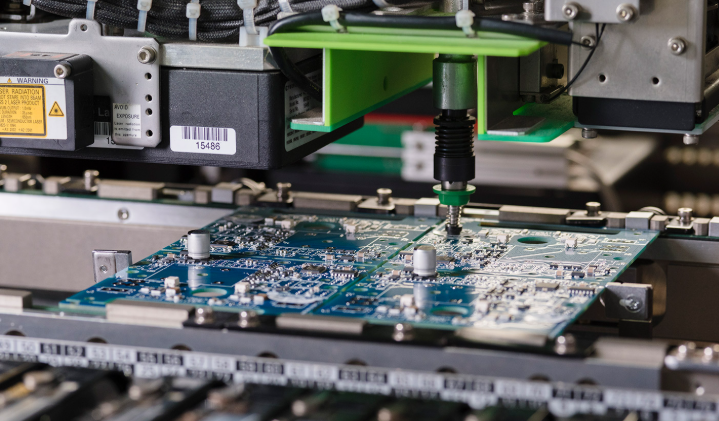

The comprehensiveness of our one-stop service ensures smooth supply chain operation by integrating pre-production DFM review, component verification, precision assembly, full-process testing, and timely delivery into a seamless process. We conduct professional DFM analysis before production to identify design mismatches that may cause mid-production modifications, avoiding delays from rework. Simultaneously, we utilize MES intelligent management systems for real-time tracking of production and logistics, dynamically adjusting production schedules based on order urgency to ensure each link is closely connected, enabling reliable on-time delivery even for urgent orders.

Why Choose EBest(Best Technology) for PCB Assembly Services Switzerland?

Reasons why choose EBst(Best Technology) for PCB assembly services Switzerland:

- 5-Year Quality Warranty: We provide a 5-year quality warranty for all our PCB assembly services Switzerland, covering manufacturing defects, soldering issues, and assembly-related component failures, offering free repair or replacement to minimize your post-delivery risks and ensure long-term product reliability.

- Advanced MES Tracking System: Our advanced MES (Manufacturing Execution System) enables real-time tracking of the entire production process, from material incoming to final delivery, supporting end-to-end traceability of materials, processes and test data for easy compliance audits and production progress inquiry.

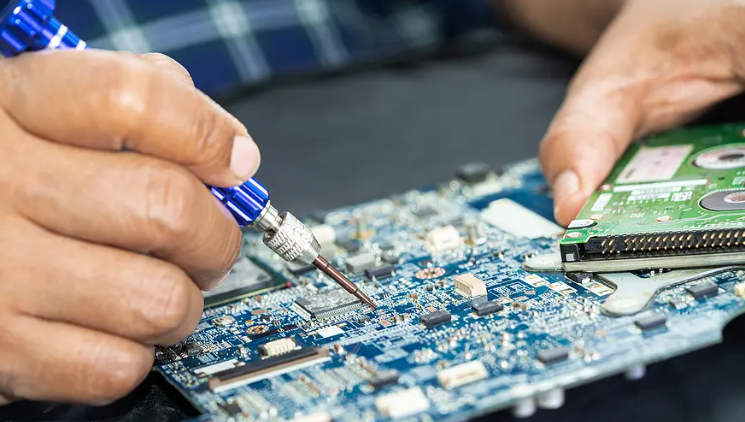

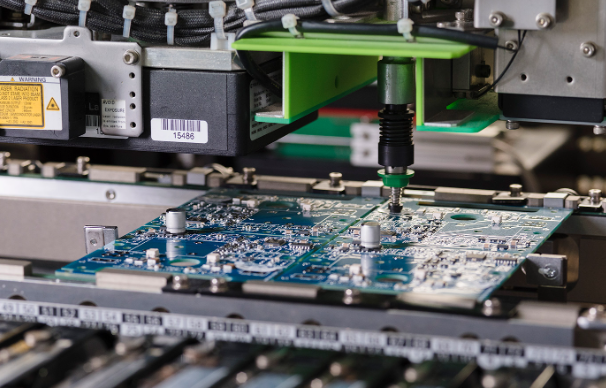

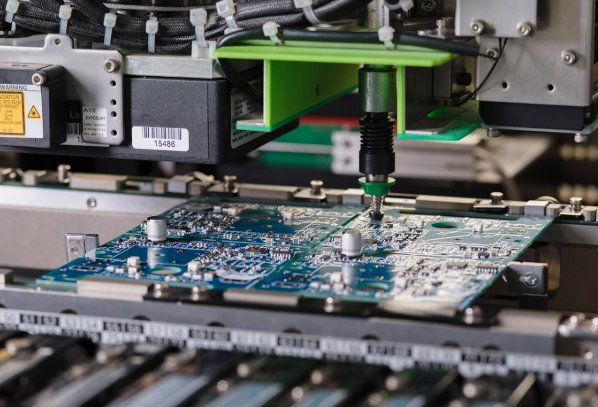

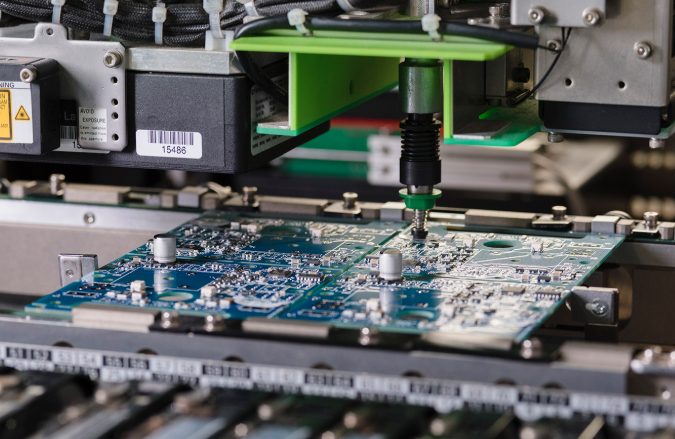

- Strict Multi-Level Quality Inspection: We implement three-level quality inspection (incoming material inspection, in-process inspection, final inspection) using AOI, X-ray and functional testing equipment, ensuring a first-pass yield of 99.8% and eliminating defective products before delivery.

- Rapid Prototype Turnaround: We offer fast prototype assembly with a 24-48 hour turnaround time and small-batch production delivery within 3-5 days, accelerating your product development cycle and helping you launch products to market faster.

- Customized Assembly Solutions: We tailor assembly processes to your unique project needs, including ultra-miniaturized components (01005), high-temperature resistant PCBA (-55°C to 125°C) and HDI boards with 10μm line/space, adapting to diverse industry requirements.

- Full Compliance Certifications: We hold ISO 9001:2015, ISO 13485:2016, and IPC-A-610 Class 3 certifications, fully meeting the strict compliance requirements of medical, industrial and high-reliability electronic fields in Switzerland.

- Transparent Pricing & No Hidden Fees: We provide detailed, itemized quotes upfront, with zero setup fees for orders over 100 units, ensuring you have clear cost control without any unexpected additional charges.

- Comprehensive Testing Services: We offer one-stop testing services including ICT, FCT, functional testing and reliability testing, verifying every PCB assembly’s performance and durability to avoid post-delivery failures.

- Global Verified Supplier Network: We cooperate with 15+ globally verified component suppliers and operate an intelligent warehousing center, ensuring stable material supply and shortening sourcing lead times to 3-5 days.

- 24/7 Dedicated Project Support: Our professional team is available 24 hours a day, 7 days a week to respond to your inquiries, update project progress and resolve any assembly-related issues promptly.

Types of PCB Assembly Services Switzerland We Offered

PCB Manufacturing Types

- Rigid/Flexible/Rigid-Flex Boards: Supports sizes ranging from 50mm to 700mm × 460mm, suitable for industrial equipment and wearable electronics.

- Custom Shaped Circuit Boards: Provides cutting of circular, rectangular, and non-transparent special-shaped PCBs to meet the needs of space-constrained applications such as medical equipment.

Production Service Modes

- Small Batch Rapid Prototyping: Equipped with a real-time MES scheduling system, responding to production line bottlenecks within 1 hour to ensure timely delivery of urgent orders.

- Medium to Large Volume Manufacturing: Coordinates component procurement through a local Swiss supply chain network (Zurich/Biel) to reduce logistics delay risks.

Value-Added Services

- Design Engineering Support: Collaborates with institutions such as CSEM to provide signal integrity optimization, compatible with high-frequency applications in automotive electronics.

- Full-Process Quality Monitoring: 100% production data traceability, compliant with ISO and CE certification standards.

- Mechatronics Assembly: Extends to the integrated assembly of precision components (such as printer heating units).

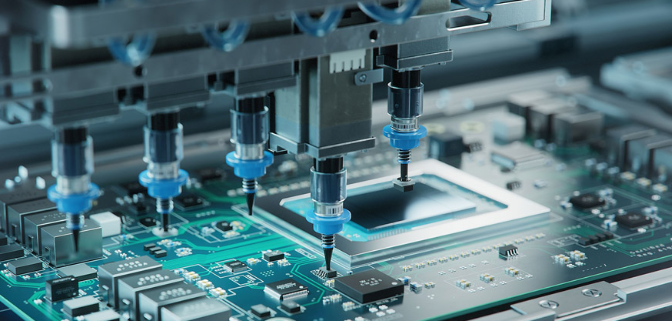

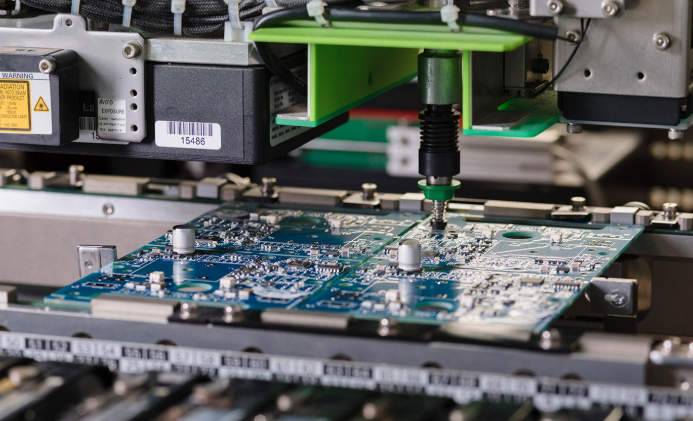

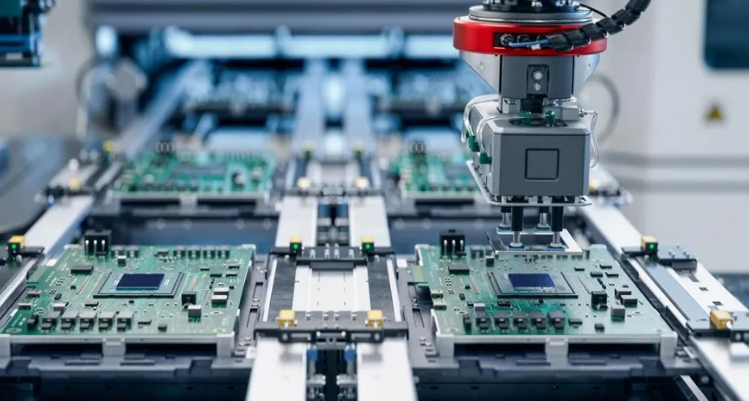

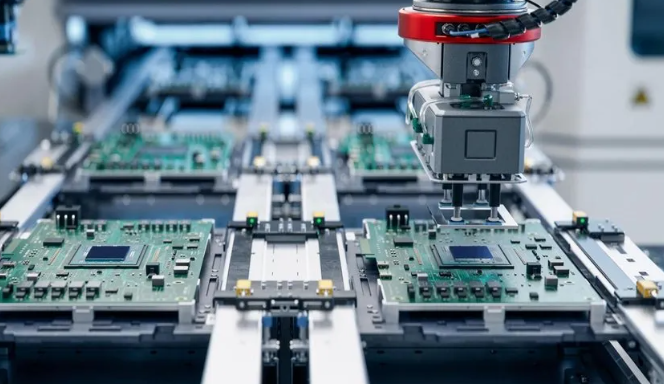

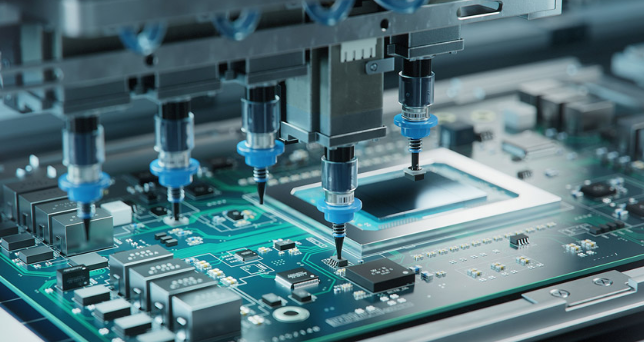

Our Switzerland PCBA Capabilities

| Item | Capabilities |

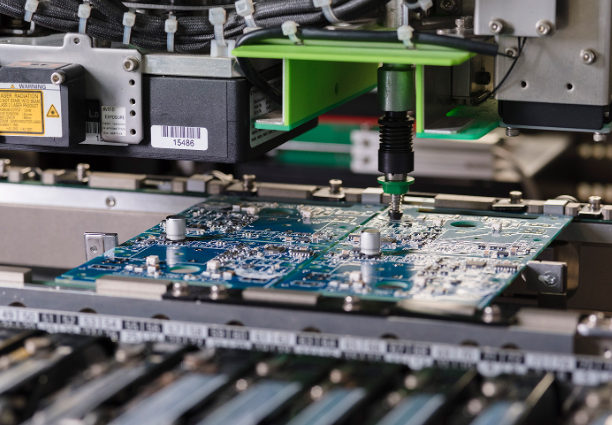

| Placer Speed | 13,200,000 chips/day |

| Bare Board Size | 0.2 x 0.2 inches – 20 x 20 inches/ 22*47.5 inches |

| Minimum SMD Component | 01005 |

| Minimum BGA Pitch | 0.25mm |

| Maximum Components | 50*150mm |

| Assembly Type | SMT, THT, Mixed assembly |

| Component Package | Reels, Cut Tape, Tube, Tray, Loose Parts |

| Lead Time | 1 – 5 days |

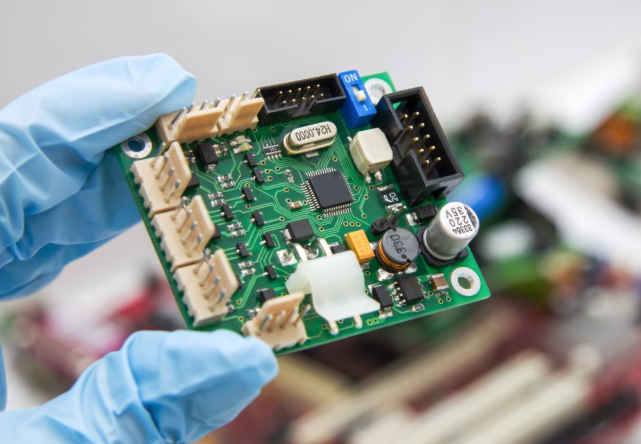

Case Studies of Medical PCB Assembly Services Switzerland

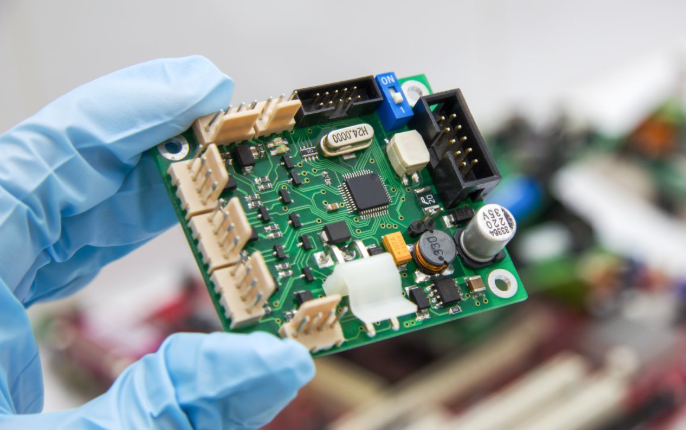

Project Background: A Swiss medical device company sought a trusted partner for assembling PCBA for their new neurostimulator. Dissatisfied with their previous provider’s inconsistent quality and missed deadlines, they needed a reliable PCB assembly services Switzerland provider meeting strict medical device manufacturing standards.

Project Requirements: Key requirements included a 12-layer rigid-flex PCB assembly, ISO 13485:2016 compliance, 99.8% first-pass yield, 14-day delivery, 30μm line/space for high-density components, and FDA certification compatibility.

Project Challenges: Critical challenges included: ±100μm layer-to-layer alignment error causing intermittent signal failure (risking FDA failure); difficult placement of small 0201 components (prone to soldering defects); and strict biocompatibility requirements for all materials.

Our Solutions: Our solutions addressed these challenges: optical alignment closed-loop control reduced alignment error to ±50μm; high-precision SMT machines ensured accurate 0201 component placement; we sourced biocompatible, RoHS-compliant materials with MES traceability; and pre-production DFM reviews prevented potential issues.

Output Results: Exceptional results: 99.9% first-pass yield, 500 units delivered 2 days early, consistent ±45μm alignment error, zero FDA pre-certification non-conformities, and a 0.05% failure rate during 6-month field trials, demonstrating our reliable PCB assembly services Switzerland.

FAQs of PCB Assembly in Switzerland

Q1: How can I ensure components used in Swiss PCBA are not counterfeit?

A1: Partner with suppliers that provide full material traceability (batch IDs, certificates of conformity) and conduct incoming inspections using X-ray and optical testing. We verify all components against IPC standards and maintain a list of 15+ verified local suppliers to eliminate counterfeit risks.

Q2: What is the typical lead time for PCB assembly services Switzerland?

A2: Lead times vary by order size: prototypes (24-48 hours), small batches (10-100 units: 3-5 days), medium batches (100-1,000 units: 7-10 days), and large batches (1,000+ units: 10-14 days). Local component warehousing can reduce lead times by 30-40%.

Q3: Is it cost-effective to use small-batch PCB assembly in Switzerland?

A3: Yes, with our zero setup fees for orders over 100 units and optimized production processes, we reduce per-unit costs by 25% for small batches. We also offer flexible pricing for repeat small-batch orders to further lower costs.

Q4: How do I ensure my PCBA meets Swiss medical device compliance standards?

A4: Work with a provider certified to ISO 13485:2016 and experienced in medical PCBA. We conduct pre-production compliance reviews, use FDA-approved materials, maintain end-to-end traceability, and provide documentation required for CE and FDA certifications.

Q5: What should I do if my PCB design has DFM issues for Swiss assembly?

A5: Request a free DFM review before production. Our team identifies design mismatches (e.g., component spacing, pad size) within 24 hours and provides actionable adjustments to optimize for Swiss assembly processes, reducing rework and delays.