# IPC-6012E 2020 - March

# Qualification and Performance Specification for Rigid Printed Boards

Supersedes IPC-6012D September 2015 An international standard developed by IPC

Association Connecting Electronics Industries

**IPC-6012E**

# Qualification and Performance Specification for Rigid Printed Boards

Developed by the Rigid Printed Board Performance Specifications Task Group (D-33a) of the Rigid Printed Board Committee (D-30) of IPC

#### Supersedes:

IPC-6012D - September 2015 IPC-6012C - April 2010 IPC-6012B with Amendment 1 - July 2007 IPC-6012B - August 2004 IPC-6012A with Amendment 1 - July 2000 IPC-6012A - October 1999 IPC-6012 - July 1996 IPC-RB-276 - March 1992 Users of this publication are encouraged to participate in the development of future revisions.

Contact:

IPC

# **Table of Contents**

| 1 SC  | <b>OPE</b>                                                                |

|-------|---------------------------------------------------------------------------|

| 1.1   | Statement of Scope 1                                                      |

| 1.2   | Purpose 1                                                                 |

| 1.2.1 | Supporting Documentation 1                                                |

| 1.3   | Performance Classification and Type 1                                     |

| 1.3.1 | Classification 1                                                          |

| 1.3.2 | Printed Board Type 1                                                      |

| 1.3.3 | Selection for Procurement 1                                               |

| 1.3.4 | Material, Plating Process and Surface Finish 3                            |

| 1.4   | Terms and Definitions 4                                                   |

| 1.4.1 | Back-Drilling                                                             |

| 1.4.2 | Stub (Plated Hole) 4                                                      |

| 1.4.3 | High Density Interconnects (HDI) 4                                        |

| 1.4.4 | Microvia 5                                                                |

| 1.4.5 | Design Data 5                                                             |

| 1.5   | Interpretation                                                            |

| 1.6   | Presentation                                                              |

| 1.7   | Design Data Protection 5                                                  |

| 1.8   | Revision Level Changes 5                                                  |

| 2 AP  | PLICABLE DOCUMENTS                                                        |

| 2.1   | IPC                                                                       |

| 2.2   | Joint Industry Standards 8                                                |

| 2.3   | Federal                                                                   |

| 2.4   | Other Publications                                                        |

| 2.4.1 | American Society for Testing and Materials 8                              |

| 2.4.2 | Underwriters Lab 8                                                        |

| 2.4.3 | National Electrical Manufacturers<br>Association                          |

| 2.4.4 | American Society for Quality 8                                            |

| 2.4.5 | AMS                                                                       |

| 2.4.6 | American Society of Mechanical Engineers 8                                |

| 3 RE  | QUIREMENTS9                                                               |

| 3.1   | General9                                                                  |

| 3.2   | Materials                                                                 |

| 3.2.1 | Laminates and Bonding Material9                                           |

| 3.2.2 | External Bonding Materials9                                               |

| 3.2.3 | Other Dielectric Materials                                                |

| 3.2.4 | Metal Foils                                                               |

| 3.2.5 | Metal Planes/Cores                                                        |

| 3.2.6 | Base Metallic Plating Depositions and<br>Conductive Coatings              |

| 3.2.7 | Surface Finish Depositions and Coatings –<br>Metallic and Non-Metallic 10 |

| 3.2.8  | Polymer Coating (Solder Mask) 1                                          | 3 |

|--------|--------------------------------------------------------------------------|---|

| 3.2.9  | Fusing Fluids and Fluxes 1                                               | 3 |

| 3.2.10 | Marking Inks 1                                                           | 3 |

| 3.2.11 | Hole Fill Insulation Material 1                                          | 3 |

| 3.2.12 | Heatsink Planes, External 1                                              | 3 |

| 3.2.13 | Via Protection                                                           | 4 |

| 3.2.14 | Embedded Passive Materials 1                                             | 4 |

| 3.3    | Visual Examination1                                                      | 4 |

| 3.3.1  | Edges 1                                                                  | 4 |

| 3.3.2  | Laminate Imperfections 14                                                | 4 |

| 3.3.3  | Plating and Coating Voids in the Hole 1                                  | 5 |

| 3.3.4  | Lifted Lands 1                                                           | 5 |

| 3.3.5  | Marking 1                                                                | 5 |

| 3.3.6  | Solderability1                                                           | 6 |

| 3.3.7  | Plating Adhesion1                                                        | 6 |

| 3.3.8  | Edge Printed Board Contact, Junction of<br>Gold Plate to Solder Finish 1 | 6 |

| 3.3.9  | Back-Drilled Holes 1                                                     | 7 |

| 3.3.10 | Workmanship1                                                             | 7 |

| 3.4    | Printed Board Dimensional Requirements 1                                 | 7 |

| 3.4.1  | Hole Size, Hole Pattern Accuracy and<br>Pattern Feature Accuracy 1       | 7 |

| 3.4.2  | Annular Ring and Breakout (External) 1                                   | 7 |

| 3.4.3  | Bow and Twist 1                                                          | 9 |

| 3.5    | Conductor Definition1                                                    | 9 |

| 3.5.1  | Conductor Width and Thickness 2                                          | 0 |

| 3.5.2  | Conductor Spacing                                                        | 0 |

| 3.5.3  | Conductor Imperfections                                                  | 0 |

| 3.5.4  | Conductive Surfaces                                                      |   |

| 3.6    | Structural Integrity 2                                                   | 2 |

| 3.6.1  | Thermal Stress Testing                                                   |   |

| 3.6.2  | Requirements for Microsectioned<br>Coupons or Printed Boards             |   |

| 3.7    | Solder Mask Requirements                                                 | 9 |

| 3.7.1  | Solder Mask Coverage                                                     |   |

| 3.7.2  | Solder Mask Cure and Adhesion                                            |   |

| 3.7.3  | Solder Mask Thickness 4                                                  |   |

| 3.8    | Electrical Requirements 4                                                | 0 |

| 3.8.1  | Dielectric Withstanding Voltage 4                                        |   |

| 3.8.2  | Electrical Continuity and Isolation<br>Resistance                        |   |

| 3.8.3  | Circuit/Plated Hole Shorts to Metal<br>Substrate                         |   |

| 3.8.4  | Moisture and Insulation Resistance (MIR) 4                               |   |

|        |                                                                          |   |

| 3.9     | Cleanliness                                                                                          | 41 |

|---------|------------------------------------------------------------------------------------------------------|----|

| 3.9.1   | Cleanliness Prior to Solder Mask<br>Application                                                      | 41 |

| 3.9.2   | Cleanliness After Solder Mask, Solder, or<br>Alternative Surface Coating Application                 | 41 |

| 3.9.3   | Cleanliness of Inner Layers After Oxide<br>Treatment Prior to Lamination                             | 41 |

| 3.10    | Special Requirements                                                                                 | 41 |

| 3.10.1  | Outgassing                                                                                           | 41 |

| 3.10.2  | Fungus Resistance                                                                                    | 41 |

| 3.10.3  | Vibration                                                                                            | 41 |

| 3.10.4  | Mechanical Shock                                                                                     | 41 |

| 3.10.5  | Impedance Testing                                                                                    | 41 |

| 3.10.6  | Coefficient of Thermal Expansion (CTE)                                                               | 42 |

| 3.10.7  | Thermal Shock                                                                                        | 42 |

| 3.10.8  | Surface Insulation Resistance<br>(As Received)                                                       | 42 |

| 3.10.9  | Metal Core (Horizontal Microsection)                                                                 | 42 |

| 3.10.10 | Rework Simulation                                                                                    | 42 |

| 3.10.11 | Bond Strength, Unsupported Component<br>Hole Land                                                    | 42 |

| 3.10.12 | Destructive Physical Analysis                                                                        | 42 |

| 3.10.13 | Peel Strength Requirements (For Foil<br>Laminated Construction Only)                                 | 42 |

| 3.10.14 | Design Data Protection                                                                               | 42 |

| 3.10.15 | Performance Based Testing for Microvia<br>Structures – Structural Integrity During<br>Thermal Stress | 43 |

| 3.11    | Repair                                                                                               |    |

| 3.11.1  | Circuit Repairs                                                                                      |    |

| 3.12    | Rework                                                                                               |    |

|         |                                                                                                      |    |

|         |                                                                                                      |    |

| 4.1     | General                                                                                              |    |

| 4.1.1   | Qualification                                                                                        |    |

| 4.1.2   | Sample Test Coupons                                                                                  |    |

| 4.2     | Acceptance Tests                                                                                     | 44 |

| 4.2.1   | C=0 Zero Acceptance Number Sampling<br>Plan                                                          | 44 |

| 4.2.2   | Referee Tests                                                                                        | 44 |

| 4.3     | Quality Conformance Testing                                                                          | 44 |

| 4.3.1   | Coupon Selection                                                                                     | 45 |

| 5 NO    | DTES                                                                                                 | 50 |

| 5.1     | Ordering Data                                                                                        |    |

| 5.2     | Superseded Specifications                                                                            |    |

| APPEN   |                                                                                                      |    |

vi

#### Figures

| Figure 1-1  | Example of a Back-Drilled Hole<br>(Not To Scale)                                                         | . 4 |

|-------------|----------------------------------------------------------------------------------------------------------|-----|

| Figure 1-2  | Example of a Shallow Back-Drill                                                                          | . 4 |

| Figure 1-3  | Microvia Definition                                                                                      |     |

| Figure 3-1  | Annular Ring Measurement (External)                                                                      | 19  |

| Figure 3-2  | Breakout of 90° and 180°                                                                                 |     |

| Figure 3-3  | External Conductor Width Reduction                                                                       | 19  |

| Figure 3-4  | Example of Intermediate Target Land in a Microvia                                                        | 19  |

| Figure 3-5  | Rectangular Surface Mount Lands                                                                          | 20  |

| Figure 3-6  | Round Surface Mount Lands                                                                                | 21  |

| Figure 3-7  | Printed Board Edge Connector Lands                                                                       | 21  |

| Figure 3-8  | Plated Hole Microsection (Grinding/<br>Polishing) Tolerance                                              | 23  |

| Figure 3-9  | An Example of Plating to Target Land<br>Separation                                                       | 23  |

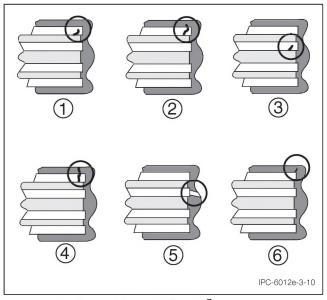

| Figure 3-10 | Copper Crack Definition                                                                                  | 26  |

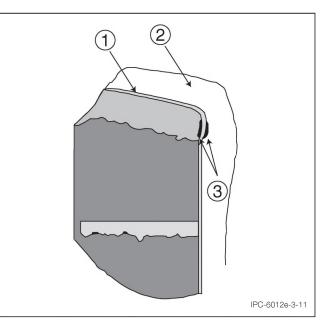

| Figure 3-11 | Separations at External Foil                                                                             | 26  |

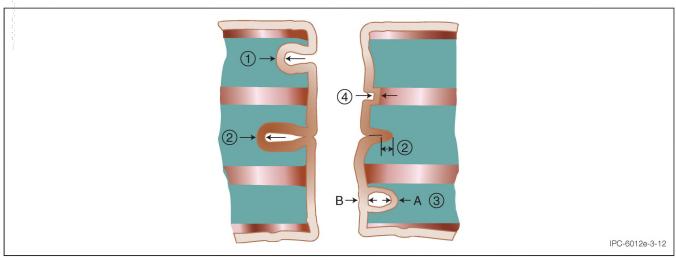

| Figure 3-12 | Plating Folds/Inclusions – Minimum<br>Measurement Points                                                 | 26  |

| Figure 3-13 | Microsection Evaluation Laminate<br>Attributes                                                           | 27  |

| Figure 3-14 | Measurement for Etchback                                                                                 | 27  |

| Figure 3-15 | Measurement for Dielectric Removal                                                                       | 28  |

| Figure 3-16 | Measurement for Negative Etchback                                                                        | 28  |

| Figure 3-17 | Annular Ring Measurement (Internal)                                                                      |     |

| Figure 3-18 | Microsection Rotations for Breakout<br>Detection                                                         |     |

| Figure 3-19 | Comparison of Microsection Rotations                                                                     | 29  |

| Figure 3-20 | Example of Non-Conforming Dielectric<br>Spacing Reduction Due to Breakout at<br>Microvia Target Land     | 30  |

| Figure 3-21 | Surface Copper Wrap Measurement for Filled Holes (Over Foil)                                             | 30  |

| Figure 3-22 | Surface Copper Wrap Measurement for Filled Holes (Over Laminate)                                         | 31  |

| Figure 3-23 | Surface Copper Wrap Measurement for Non-Filled Holes                                                     | 31  |

| Figure 3-24 | Wrap Copper (Acceptable)                                                                                 | 31  |

| Figure 3-25 | Wrap Copper Removed by Excessive<br>Processing, e.g., Sanding/Planarization/<br>Etching (Not Acceptable) | 32  |

| Figure 3-26 | Copper Cap Thickness                                                                                     | 33  |

| Figure 3-27 | Copper Cap Filled Via Height (Bump)                                                                      | 33  |

| Figure 3-28 | Copper Cap Depression (Dimple)                                                                           | 33  |

| Figure 3-29 | Copper Cap Plating Voids                                                                                 |     |

| Figure 3-30 | Nonconforming Via Fill Between Copper<br>Cap Plating Layers                                              | 33  |

| Figure 3-31 | Acceptable Via Fill Between Copper Cap<br>Plating Layers                                                 |     |

| Figure 3-32 | Example of Acceptable Voiding in a Cap<br>Plated, Copper Filled Via                                      | 34  |

| Figure 3-33 | Example of Acceptable Voiding in a Copper<br>Filled Microvia without Cap Plating     |

|-------------|--------------------------------------------------------------------------------------|

| Figure 3-34 | Example of Nonconforming Void in a Cap<br>Plated, Copper Filled Microvia             |

| Figure 3-35 | Example of Nonconforming Void in a<br>Copper Filled Microvia                         |

| Figure 3-36 | Microvia Contact Dimension 35                                                        |

| Figure 3-37 | Exclusion of Separations in Microvia<br>Target Land Contact Dimension                |

| Figure 3-38 | Unintended Piercing of Microvia Target<br>Land (Laser Drilled)                       |

| Figure 3-39 | Intentional Piercing of Microvia Target<br>Land (Mechanically Drilled <sup>2</sup> ) |

| Figure 3-40 | Overhang                                                                             |

| Figure 3-41 | Metal Core to PTH Spacing 37                                                         |

| Figure 3-42 | Measurement of Minimum Dielectric<br>Spacing                                         |

| Figure 3-43 | Fill Material in Blind/Through Vias<br>When Cap Plating Not Specified                |

| Figure 3-44 | Void in Fill Material at Hole Wall Interface 38                                      |

#### Tables

| Table 1-1 | Technology Adders 2                                  |

|-----------|------------------------------------------------------|

| Table 1-2 | Default Requirements 3                               |

| Table 3-1 | Metal Planes/Cores9                                  |

| Table 3-2 | Maximum Limits of SnPb Solder Bath<br>Contaminant 10 |

| Table 3-3 | Surface Finish and Coating Requirements 12           |

| Table 3-4  | Surface and Hole Copper Plating Minimum<br>Requirements for Buried Vias > 2 Layers,<br>Through-Holes, and Blind Vias |

|------------|----------------------------------------------------------------------------------------------------------------------|

| Table 3-5  | Surface and Hole Copper Plating<br>Minimum Requirements for Microvias<br>(Blind and Buried)13                        |

| Table 3-6  | Surface and Hole Copper Plating Minimum<br>Requirements for Buried Cores (2 layers) 13                               |

| Table 3-7  | Plating and Coating Voids in the Hole 15                                                                             |

| Table 3-8  | Edge Printed Board Contact Gap 17                                                                                    |

| Table 3-9  | Minimum Annular Ring 18                                                                                              |

| Table 3-10 | Plated Hole Integrity After Stress 25                                                                                |

| Table 3-11 | Cap Plating Requirements for Filled Holes 32                                                                         |

| Table 3-12 | Microvia Contact Dimension (Laser Drilled) 35                                                                        |

| Table 3-13 | Microvia Contact Dimension<br>(Mechanically Drilled)                                                                 |

| Table 3-14 | Internal Layer Foil Thickness after<br>Processing                                                                    |

| Table 3-15 | External Conductor Thickness after<br>Plating                                                                        |

| Table 3-16 | Solder Mask Adhesion 40                                                                                              |

| Table 3-17 | Dielectric Withstanding Voltages 40                                                                                  |

| Table 3-18 | Insulation Resistance 40                                                                                             |

| Table 4-1  | Qualification Test Coupons 44                                                                                        |

| Table 4-2  | C=0 Sampling Plan per Lot Size 45                                                                                    |

| Table 4-3  | Acceptance Testing and Frequency 46                                                                                  |

| Table 4-4  | Quality Conformance Testing 50                                                                                       |

### **Qualification and Performance Specification for Rigid Printed Boards**

#### 1 SCOPE

**1.1 Statement of Scope** This specification establishes and defines the qualification and performance requirements for the fabrication of rigid printed boards.

**1.2 Purpose** The purpose of this specification is to provide requirements for qualification and performance of rigid printed boards based on the following constructions and/or technologies. These requirements apply to the finished product unless otherwise specified:

- Single-sided, double-sided printed boards with or without plated-through holes (PTHs).

- Multilayer printed boards with PTHs with or without buried/blind vias/microvias.

- Active/passive embedded circuitry printed boards with distributive capacitive planes and/or capacitive or resistive components.

- Metal core printed boards with or without an external metal heat frame, which may be active or non-active.

**1.2.1 Supporting Documentation** IPC-A-600, which contains figures, illustrations and photographs that can aid in the visualization of externally and internally observable acceptable/nonconforming conditions, may be used in conjunction with this specification for a more complete understanding of the recommendations and requirements.

#### **1.3 Performance Classification and Type**

**1.3.1 Classification** This specification establishes acceptance criteria for the performance classification of rigid printed boards based on customer and/or end-use requirements. Printed boards are classified by one of three general Performance Classes as defined in IPC-6011.

**1.3.1.1 Requirement Deviations** Requirements deviating from these heritage classifications **shall** be as agreed between user and supplier (AABUS).

**1.3.1.2 Space Requirement Deviations** Space performance classification deviations are provided in the IPC-6012ES Addendum and are applicable when the addendum is specified within the procurement documentation.

**1.3.2 Printed Board Type** Printed boards without PTHs (Type 1) and with PTHs (Types 2-6) are classified as follows and may include technology adders as described in Table 1-1:

- Type 1 Single-Sided Printed Board

- Type 2 Double-Sided Printed Board

- *Type 3* Multilayer Printed Board without blind or buried vias

- *Type 4* Multilayer Printed Board with blind and/or buried vias (may include microvias)

- Type 5 Multilayer metal core Printed Board without blind or buried vias

- *Type 6* Multilayer metal core Printed Board with blind and/or buried vias (may include microvias)

1.3.3 Selection for Procurement Performance Class shall be specified in the procurement documentation.

The procurement documentation **shall** provide sufficient information to fabricate the printed board and ensure that the user receives the desired product. Information that should be included in the procurement documentation is to be in accordance with IPC-2611 and IPC-2614.

The procurement documentation **shall** specify the thermal stress test method to be used to meet the requirement of 3.6.1. Selection **shall** be from those depicted in 3.6.1.1, 3.6.1.2 and 3.6.1.3. If not specified (see 5.1), the default **shall** be per Table 1-2.

When tested in accordance with IPC-TM-650, Method 2.4.28.1, the maximum percentage of cured solder mask lifting from the G coupon or printed board **shall** be in accordance with Table 3-16.

|                                                                        | Maximum Percentage Loss Allowed |         |         |

|------------------------------------------------------------------------|---------------------------------|---------|---------|

| Surface                                                                | Class 1                         | Class 2 | Class 3 |

| Bare Copper                                                            | 10                              | 5       | 0       |

| Gold or Nickel                                                         | 25                              | 10      | 5       |

| Base Laminate                                                          | 10                              | 5       | 0       |

| Melting Metals (Tin-lead plating, fused tin-lead, and bright acid-tin) | 50                              | 25      | 10      |

| Table 3-16 | Solder | Mask | Adhesion |

|------------|--------|------|----------|

| 10010 0 10 |        |      |          |

**3.7.3 Solder Mask Thickness** Any requirement for the measurement of solder mask thickness **shall** be AABUS. If a thickness measurement is required, instrumental methods may be used or assessment may be made using a microsection of the parallel conductors on the E coupon or Destructive Physical Analysis (DPA) (see 3.10.12, thermal stress not required). For additional guidance on solder mask thickness measurement options, see the IPC-6012 Automotive Addendum.

**3.8 Electrical Requirements** When tested as specified in Table 4-3 and Table 4-4, the printed boards **shall** meet the electrical requirements detailed in the following paragraphs.

**3.8.1 Dielectric Withstanding Voltage** Applicable test coupons or printed boards **shall** meet the requirements of Table 3-17, without flashover, or breakdown between conductors, or conductors and lands. The dielectric withstanding voltage test **shall** be performed in accordance with IPC-TM-650, Method 2.5.7. The dielectric withstanding voltage **shall** be applied between all common portions of each conductor pattern and adjacent common portions of each conductor pattern. The voltage **shall** be applied between conductor patterns of each layer and the electrically isolated pattern of each adjacent layer. For embedded passive device capacitor materials, the dielectric withstanding voltage for adjacent plane layers that are not electrically common **shall** be per IPC-6017.

| Table 3-17 | Dielectric | Withstanding | Voltages |

|------------|------------|--------------|----------|

|------------|------------|--------------|----------|

|                                                  | Class 1        | Class 2 and Class 3 |

|--------------------------------------------------|----------------|---------------------|

| Voltage for Spacing 80 µm [3,150 µin] or greater | No requirement | (500 +15 -0) V (dc) |

| Voltage for Spacing less than 80 µm [3,150 µin]  | No requirement | (250 +15 -0) V (dc) |

| Time                                             | No requirement | 30 sec +3, -0       |

**3.8.2 Electrical Continuity and Isolation Resistance** Finished printed boards **shall** be tested in accordance with IPC-9252. Electrical continuity and isolation resistance testing of blind and buried structures is not required for in process checks.

**3.8.3 Circuit/Plated Hole Shorts to Metal Substrate** Printed boards **shall** be tested in accordance with 3.8.1 except that polarizing voltage of (500 + 15 - 0) V (dc) **shall** be applied between conductors and/or lands and the metal substrate (heat sink or core) in a manner such that each conductor/land area is tested (e.g., using a metallic brush or aluminum foil). The printed board **shall** be capable of withstanding (500 +15 -0) V (dc) between circuitry/plated holes and the metal core substrates. There **shall** be no flashover or dielectric breakdown.

**3.8.4 Moisture and Insulation Resistance (MIR)** Test coupons **shall** be tested in accordance with the procedure outlined below. The test coupon **shall not** exhibit subsurface imperfections in excess of that allowed in 3.3.2. Insulation resistance **shall** meet the minimum requirements shown in Table 3-18 (at (500 +15 -0) V (dc)). Non-component flush printed boards **shall** have a minimum requirement of 50 M $\Omega$  for all classes.

|                            | Class 1                      | Class 2 | Class 3 |

|----------------------------|------------------------------|---------|---------|

| As received <sup>1</sup>   | Maintain electrical function | 500 MΩ  | 500 MΩ  |

| After exposure to moisture | Maintain electrical function | 100 MΩ  | 500 MΩ  |

Table 3-18 Insulation Resistance

Note 1. This measurement is taken after conformal coating material has been applied to the test coupon in accordance with IPC-TM-650, Method 2.6.3.

The moisture and insulation resistance for printed boards **shall** be performed in accordance with IPC-TM-650, Method 2.6.3. Conformal coating in accordance with IPC-CC-830 **shall** be applied to the external conductors prior to chamber exposure. Final measurements **shall** be made at room temperature within two hours after removal from the test chamber. All layers

版权等原因,不能全部发布。 此为样本文件,如需更多内容,完整版: <u>单击进入</u>

# www.file123.top 1395833280@qq.com 微信: IPCSTD

#### Figure 3-10 Copper Crack Definition<sup>7</sup>

Note 1. "A" cracks - crack in external foil.

Note 2. "B" cracks - crack does not completely break plating.

Note 3. "C" cracks - crack in internal foil.

Note 4. "D" cracks - complete fracture.

Note 5. "E" cracks - barrel crack in plating only.

Note 6. "F" cracks - corner crack in plating only.

Note 7: Copper plating as shown may include multiple plating layers or cap plating.

Figure 3-11 Separations at External Foil

Note 1. Conductive coatings.

Note 2. Electrolytic copper.

Note 3. Area of acceptable separation along the vertical edge of the external foil.

#### Figure 3-12 Plating Folds/Inclusions – Minimum Measurement Points

Note 1. Minimum copper plate measurement point. Plating folds that are not enclosed and where the minimum copper plate thickness in Tables 3-4, 3-5, or 3-6 is met are acceptable.

Note 2. Enclosed plating folds (inclusions) with demarcation line visible. Measure and accept per Note 1.

Note 3. Enclosed plating fold with no visible demarcation line. The thickness measurement A+B shall comply with the minimum copper plate thickness in Tables 3-4, 3-5, or 3-6.

Note 4. Minimum copper plate measurement point for negative etchback.

**3.6.2.3 Laminate Voids** For Class 2 and Class 3 products, there **shall** be no laminate voids outside of any thermal zones (see Figure 3-13) in excess of 80  $\mu$ m [3,150  $\mu$ in]. For Class 1 products, voids allowed outside of any thermal zone (see Figure 3-13) **shall not** exceed 150  $\mu$ m [5,906  $\mu$ in]. Boundary line voids that overlap into a thermal zone **shall not** be in excess of 80  $\mu$ m [3,150  $\mu$ in] for Class 2 or Class 3 products and 150  $\mu$ m [5,906  $\mu$ in] for Class 1 products. Multiple voids between two adjacent plated holes in the same plane **shall not** have a combined length which exceeds these limits. Voids between conductive patterns that are not electrically common in either the horizontal or vertical direction **shall not** decrease the minimum dielectric spacing.

# **Benefits of IPC Membership**

## Market Your Business

USE IPC'S GLOBAL reach and exclusive member benefits to increase your company's visibility.

- Build your brand by using the IPC member logo to highlight your company's involvement, plus get free links from IPC's Web site to your Web site.

- Be listed in IPC's online membership directory available to all IPC members.

- Put your products, services and qualifications in front of key customers with a listing in IPC's Products and Services Index (PCB and EMS companies only).

- Exhibit in IPC's annual trade show and conference, IPC APEX EXPO, plus the IPC Midwest Conference & Exhibition at a special member price.

- Gain valuable exposure by sponsoring market research conferences and Management Meetings at discounted rates.

## Contain Costs

**TAKE ADVANTAGE OF** exclusive savings opportunities that can easily offset your annual membership investment.

- Get discounts of up to 50 percent on IPC standards, publications and training materials.

- Save money on subscription purchases of IPC standards through IHS. Save up to 25 percent.

- Enjoy dramatic discounts on registration fees for meetings, technical conferences, workshops and tutorials.

- Benefit from preferred pricing on exhibit space at IPC trade shows and events.

# Join the Leaders in IPC

WHATEVER SEGMENT OF the industry you are in — PCB design, board manufacturing, electronics manufacturing services (EMS), original equipment manufacturer (OEM), industry supplier, government agency, educational institution — IPC membership has something to offer virtually everyone at your site. Put the resources of the entire industry behind your company by joining IPC today!

For more than 50 years, company leaders have looked to IPC – Association Connecting Electronics Industries<sup>®</sup> for the tools, information and forums they need to thrive in the ever-changing electronic interconnect industry.

As a member-driven organization and leading source for industry standards, training, market research and public policy advocacy, IPC supports programs to meet the needs of the estimated \$1.5 trillion (U.S. dollars) global electronics industry.

Whatever your role in the industry — a small start-up company, an educational or government institution or a Fortune<sup>®</sup> 500 firm — you can join more than 2,700 companies worldwide that enjoy access to unparalleled opportunities to participate in and shape the direction of our collective future.

> To learn more about IPC membership and apply online, visit www.ipc.org.

# Put IPC Membership to Work for YOU

# Stay Current

**BE INFORMED OF** what's happening in the industry now and in the future ... and what you need to do to prepare and respond.

- Get FREE access to members-only online resources, including a searchable archive of original articles on the latest technical issues and industry/market trends.

- Access market research studies and reports and learn about the latest trends in markets and technology through IPC market research. Participate in statistical programs available for EMS, PCB, laminate, process consumables, solder and assembly equipment. Conferences are held each year in Asia, Europe and North America.

- Attend IPC workshops and educational conferences held throughout the year at special member rates.

- Stay abreast of critical technology changes and supply chain challenges stemming from global environmental directives, legislation and regulations.

# Get Connected

**NETWORK WITH YOUR** peers, and put the resources of a global industry behind your most challenging technical and business issues.

- Get involved in committees and PCB/EMS management councils to help direct the future of the industry.

- Participate in problem-solving exchanges on a vast range of industry-specific issues and concerns through IPC's technical e-mail forums.

- Network with other industry professionals at premier industry events such as the international IPC APEX EXPO as well as the regional IPC Midwest Conference & Exhibition.

- Get priority responses to your technical questions from IPC's technical staff.

# Shape the Industry

**BECOME PART OF** a worldwide network of professionals who are actively involved in shaping the future of our industry.

- Participate in developing industry standards your company, customers, competitors and suppliers use. IPC standards are internationally accepted due to affiliation with the American National Standards Institute (ANSI) and International Electrotechnical Commission (IEC).

- Make your voice heard in the regulations that affect your company by taking advantage of IPC-organized environmental and public policy activities.

# Train Your People

**INCREASE YOUR KNOWLEDGE** and facilitate continuous learning among your technical staff.

- Attend any of the 75-plus workshops and international conferences IPC sponsors annually, where the exchange of technical information is unequalled.

- Participate in IPC's voluntary training and certification programs for a cost-effective, industry-recognized way to demonstrate your commitment to quality.

- Purchase IPC's award-winning CD- and DVD-based training materials at a discount, to cost-effectively build the foundation of your company's training program.